## UNIVERSITA' DEGLI STUDI DI SALERNO

## DEPARTMENT OF PHYSICS "E. R. CAIANIELLO"

#### DOCTOR OF PHILOSOPHY IN PHYSICS

XXXII CICLO (2016-2019)

Ph.D. Thesis in

# GRAPHENE/SILICON SCHOTTKY DIODE

**GIUSEPPE LUONGO**

SUPERVISOR

PROF. ANTONIO DI BARTOLOMEO

COORDINATOR

PROF. CARMINE ATTANASIO

ACADEMIC YEAR 2019/2020

#### **Abstract**

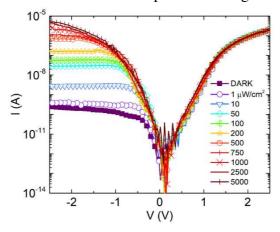

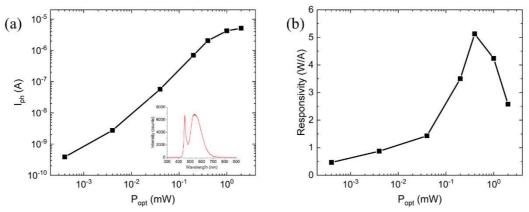

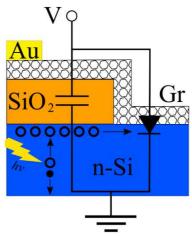

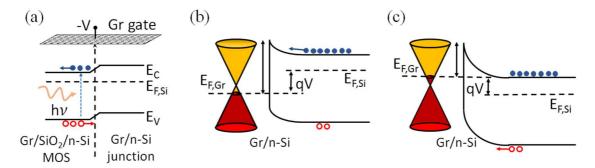

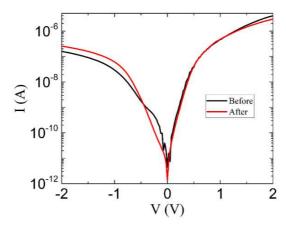

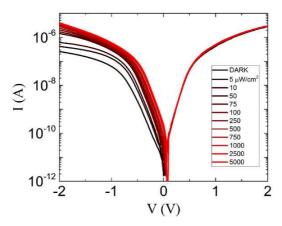

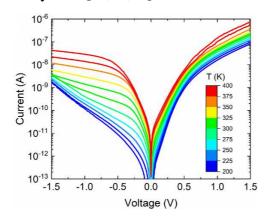

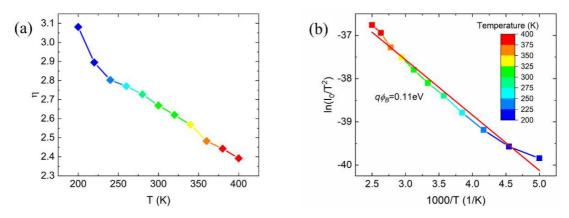

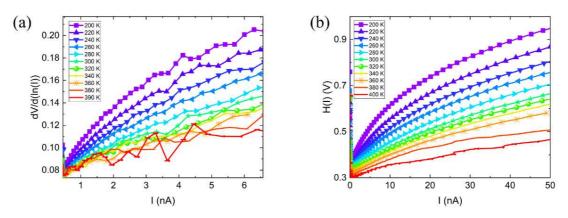

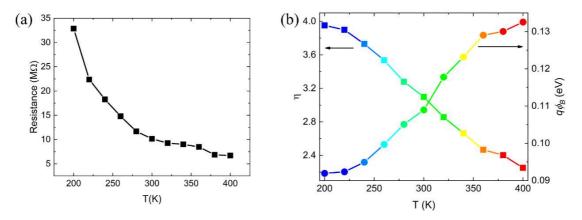

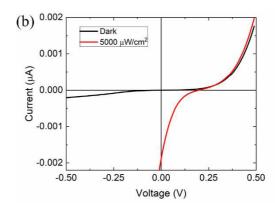

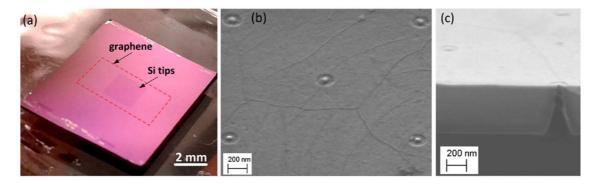

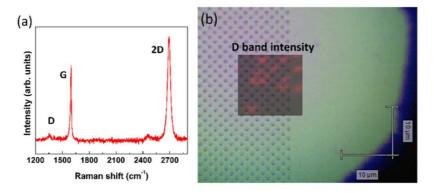

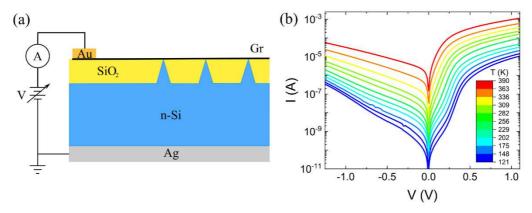

In this works we fabricated four graphene/silicon heterojunctions, which differ for structure and substrate type, and performed electrical and optical characterization. The first device was realized by depositing a layer of graphene on a trench patterned low n-doped silicon substrate. We obtained a graphene/silicon Schottky diode connected in parallel with a graphene/oxide/silicon MOS (Metal Oxide Semiconductor) capacitor. The device shows a rectification factor of 3 orders of magnitude and a Schottky barrier of 0.56 eV. The device displays a reverse current greater than the forward one when exposed to white LED light. We explained this phenomenon by taking into account the MOS capacitor connected in parallel which act as a reservoir of charges. The second device presents the same structure, but a low p-doped silicon substrate was used. In this case, we obtained a Schottky barrier of 0.17 eV which tends to get smaller when annealed to high temperature. This behaviour has been attributed to the boron atoms which diffuse from the silicon to graphene inducing a p-doping, which further reduce the Schottky barrier. The third device was realized by depositing a graphene layer on a pillar-patterned high ndoped silicon substrate. The device shows a Schottky barrier of 0.11 eV and a reverse current which grows exponentially respect to the bias. We explained this result by considering the pillar structure which, magnifying the electric field around its corners, favours the up-shift (down-shift) of the graphene Fermi level reducing (or increasing) the Schottky barrier upon application of a bias. At higher temperature this behaviour tends to disappear since the Schottky barrier variations are overcome by the thermal effects. The last device was fabricated by depositing a graphene layer on a matrix of silicon tips. The device shows a Schottky barrier of 0.36 eV which corresponds to a rectification factor of almost three orders of magnitude and a reverse current which grows exponentially with the bias over the whole temperature range. Similar to the previous junction, the tip geometry magnifies the electric field and allows to tune the Schottky barrier by changing the bias. The device shows an ideality factor closer to the unity meaning that the tip geometry reduces the formation of inhomogeneity, which can affect the junction properties, and allows the formation of higher Schottky barrier.

## Index

| Ir | ntroduc           | tion                                                | 1  |

|----|-------------------|-----------------------------------------------------|----|

| 1  | Gra               | phene                                               | 5  |

|    | 1.1               | Introduction                                        | 5  |

|    | 1.2               | Graphene electronics properties                     | 6  |

|    | 1.3               | Graphene conductivity and mobility                  | 9  |

|    | 1.4               | Graphene Doping                                     | 12 |

|    | 1.4.              | 1 Substitutional doping                             | 12 |

|    | 1.4.              | 2 Surface doping                                    | 12 |

|    | 1.4.              | .3 Electrical doping                                | 12 |

|    | 1.5               | Optical properties                                  | 12 |

|    | 1.6               | Graphene Synthesis                                  | 14 |

|    | 1.7               | Graphene Wet Transfer Process                       | 15 |

| 2  | Schottky Junction |                                                     | 19 |

|    | 2.1               | Equilibrium in electronic system                    | 19 |

|    | 2.2               | Ideal Metal-Semiconductor Junction                  | 20 |

|    | 2.3               | Interface states                                    | 23 |

|    | 2.4               | Image force lowering                                | 25 |

|    | 2.5               | Current voltage characteristic                      | 27 |

|    | 2.5.              | 1 Thermionic Emission Current                       | 28 |

|    | 2.5.              | 2 Tunneling Current                                 | 30 |

|    | 2.5.              | 3 Effect of the bias dependence of Schottky barrier | 31 |

|    | 2.5.              | 4 MIS Tunnel Diode                                  | 32 |

|    | 2.6               | Measurement of the Schottky parameters              | 33 |

|    | 2.6.              | 1 The Cheung and Cheung method                      | 34 |

|    | 2.6.              | 2 Lien-Norde method                                 | 34 |

|    | 2.6.              | Pros and cons of the methods                        | 35 |

|    | 2.7               | Capacitance-Voltage measurement                     | 35 |

| 3  | Gra               | phene/Silicon Junction                              | 37 |

|    | 3.1               | Modelling of Graphene/Silicon Junction              | 37 |

|    | 3.1.              | 1 Graphene/Silicon Photodetector                    | 40 |

|    | 3.2               | Graphene/n-Silicon Planar Junction                  | 41 |

|    | 3.2.              | 1 Device fabrication                                | 41 |

|    | 3.2.              | 2 Device electrical characterization                | 42 |

|    | 3.2.              | 3 Optical characterization                          | 45 |

| 3.2.4              | Parasitic MOS Capacitor                        | 46 |

|--------------------|------------------------------------------------|----|

| 3.3 G <sub>1</sub> | r/p-Silicon planar junction                    | 48 |

| 3.3.1              | Device fabrication                             | 48 |

| 3.3.2              | Electrical characterization                    | 49 |

| 3.3.3              | Conclusion                                     | 54 |

| 4 Graphe           | ene/Patterned Silicon Substrate Schottky Diode | 57 |

| 4.1 G              | raphene/pillar Silicon Junction                | 57 |

| 4.1.1              | Device fabrication                             | 57 |

| 4.1.2              | Electrical characterisation                    | 58 |

| 4.2 G1             | raphene/Silicon-tip Junction                   | 63 |

| 4.2.1              | Gr/Si-tip Schottky Diode Fabrication           | 63 |

| 4.2.2              | Electrical characterization                    | 65 |

| Bibliograph        | ny                                             | 72 |

#### Introduction

In the last decades, the growing demand of fastest and smallest devices has pushed the scientific community to look for a new non silicon-based technology. This technology has yet to be invented, but the discovery of the bidimensional materials, such as graphene [1], MoS<sub>2</sub> [2,3], WSe<sub>2</sub> [4,5] and phosphorene [6], etc. could be a good starting point for its achievement.

Of all bidimensional material, graphene looks like the most promising one. Theorized by Philip Wallace, which studied its band structure in 1947 [7], it was firstly produced by the chemist Hans-Peter Bohen in 1962 from graphene oxide. Because of the high fabrication cost and difficulty to obtain high quality monolayer, graphene could not spark the interest of the scientific community. It was only in 2004 when Prof Geim and Prof. Novoselov were able to obtain high-quality graphene monolayer from graphite using, what is usually referred now as the "scotch tape" method [1]. Later, new fabrication methods were discovered. Graphene layer can be grown from silicon carbide or by chemical vapour deposition (CVD) using carbon-based gas [8]. The possibility to realize large area high-quality monolayer and the compatibility with the integrated circuit fabrication process has attracted great interest as graphene could be the first step in the direction to realize the new technology that the scientific community is looking for [9].

Graphene can carry higher density current than copper, possesses higher carrier mobility than silicon [10], is stronger than steel [11], can form low contact resistance [12–14] and has low optical absorption coefficient [15] and offers the largest possible contact area which makes it an ideal platform for sensing applications. Because of its conic bandgap-less structure [7,16,17], graphene can absorb light across a broad spectrum, from the UV to the IR wavelengths [15,18]. All these properties make it suitable to realize a new generation of semiconductor devices starting from transistors [13,19–25] to Schottky diodes [16,26–32], photodetectors, solar panels [9,15,33–38] and chemical sensors [39–41].

Graphene/Silicon (Gr/Si) heterojunctions are the simplest device that can be realized. One of the first graphene/SiC Schottky junction was realized and characterized in 2009 by Filippo Giannazzo from the National Research Council in Catania, Italy, and his group [42]. And the next year Xinming Li from Beijing University and his group realized Gr/Si Schottky solar cell using CVD grown graphene on a silicon substrate [43]. Chun-Chung Chen from California University et al. realized two Gr/Si Schottky diodes by transferring mechanically exfoliated graphene on a n- and p-doped silicon substrate [26]. Later, a Gr/Si diode was realized by transferring CVD grown graphene on p-silicon substrate by Y. An et al. [44].

Gr/Si junctions offer the opportunities to study the physics occurring at the interface between a 2D and a 3D material, as well as, between a zero and a defined bandgap system and it can be the platform to investigate electronic properties and transport mechanism. Because of the graphene semimetallic behaviour, Gr/Si heterojunction current-voltage (I-V) characteristic shows a rectification behaviour which can be roughly described using the ideal diode equation. In fact, Gr/Si shows a higher saturation current density than a commercial Schottky diode [45,46]. As, we will see later, this behaviour is due to the absence of the band gap and the low-density state close to the Dirac point. The possibility to control the Schottky barrier

formed at the Gr/Si interface can be exploited to realize tunable photosensor able to detect wider wavelength range than traditional diodes.

In this work I present the results of four selected Gr/Si Schottky diodes which were realized in collaboration with the Innovation for High Performance (IHP) Microelectronics centre in Frankfurt Oder, Germany. The devices were chosen based on their I-V characteristic, optical response and substrate doping and geometry.

This work is structured in the following way: In the first chapter, I will describe graphene properties. I will briefly discuss graphene electronic properties focusing on its honeycomb lattice, band structure and electrical conductivity. Then I will describe the most common way used to dope a graphene layer and its optical properties. I will conclude the chapter discussing the different methods used to fabricate graphene monolayer and how to transfer it on a substrate.

In the second chapter, I will cover the physical phenomena and the current transport mechanism in a metal/n-doped semiconductor junction. I will conclude by describing the most common methods used to determinate all the Schottky parameters.

In the third chapter I will start by introducing the Gr/Si junction band structure, the model firstly introduced by S. Tongay to described the junction I-V characteristic [46] and then I will conclude by briefly discussing the optical properties of the junction.

After that, I will introduce the two Gr/Si planar junctions that I have been studying.

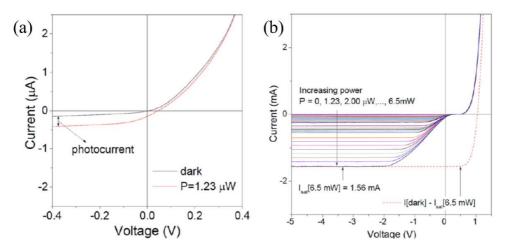

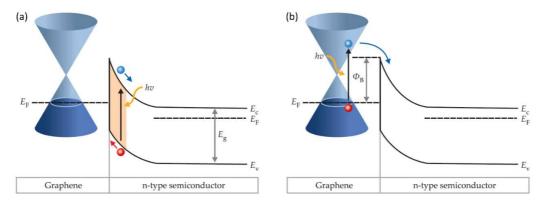

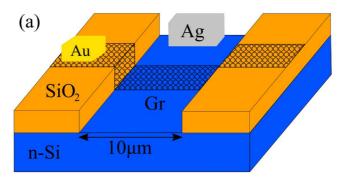

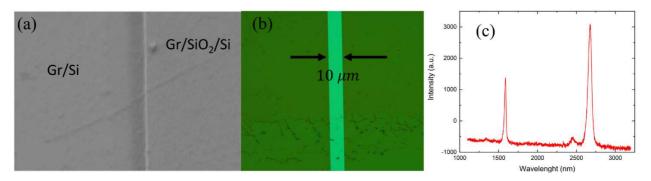

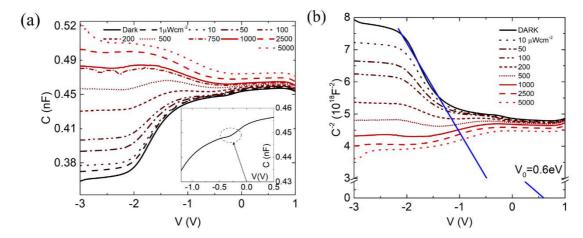

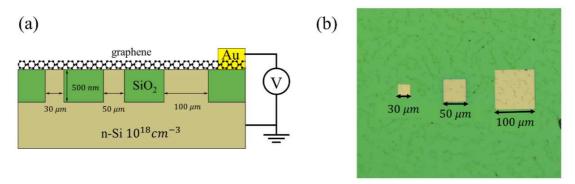

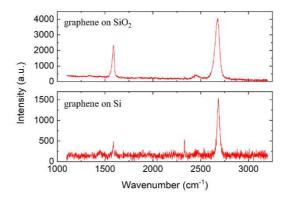

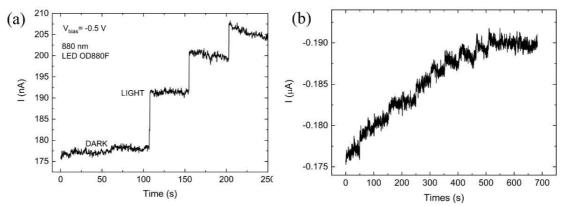

The first Gr/Si planar junction was fabricated starting from a low n-doped silicon substrate on which an oxide layer was deposited by CVD. A strip of few micrometres was patterned by lithography and a graphene monolayer large enough to cover part of the strip and the oxide was deposited on the top. I-V characteristics were measured at different temperature and in low vacuum, and at different illumination levels. The Gr/n-Si planar junction shows a Schottky barrier of 0.46 eV in agreement with the one reported in literature. The novelty of the junction is the photocurrent which is higher than the forward current at high intensity illumination level. The high photocurrent is due to the graphene/oxide/semiconductor heterostructure which acts as a metal/oxide/semiconductor (MOS) capacitor. The MOS capacitor attract the photogenerated charge between the semiconductor and the oxide layer forming a reservoir which contributes to the Gr/Si photocurrent. This hypothesis has been later confirmed by other groups [33,34].

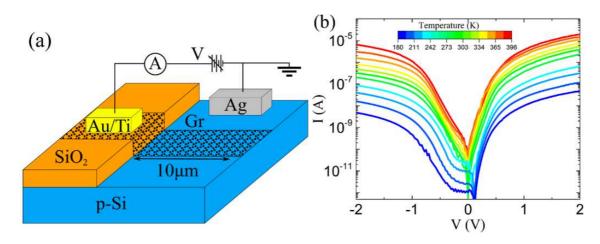

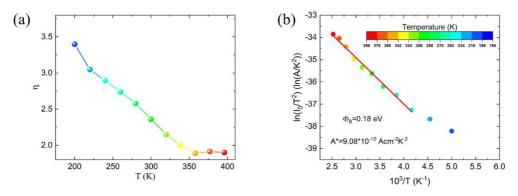

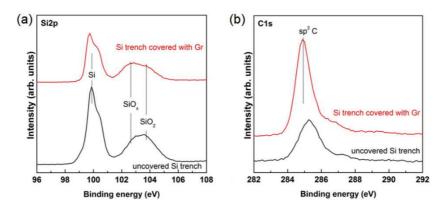

The second Gr/Si planar junction was fabricated in the same way of the previous one, but a low p-doped silicon substrate was used. The Gr/p-Si junction possesses a Schottky barrier of 0.11 eV. The low Schottky barrier is the result of the junction between two p-doped semiconductors. When graphene is exposed to the atmosphere, it shows a p-doped behaviour thus the Fermi level is shifted down the Dirac point and close to the silicon valence band. Also, we observed a reduction of the Schottky barrier and of the rectification factor after the annealing treatment at 400 K. This degradation is due to the boron atom in the silicon substrate and the graphene lattice inhomogeneity. The boron atoms are weakly bonded to the silicon ones and when enough energy is given to the system, in this case by raising the system temperature, they can out-diffuse and place themselves in the graphene lattice. The boron atoms p-dope the graphene and shift its Fermi level further down reducing the Schottky barrier [47].

In the last chapter, I will show the result obtained by characterized two graphene patterned silicon junctions. In the first Gr/Si patterned junction, three pillars with different size and the same size were patterned on a high doped silicon substrate. An oxide layer was CVD grown until it covered the pillar and it was then partially removed by CMP (Chemical-Mechanical Polishing) until the pillars surface were exposed. The I-V characteristic was measured at different temperature in low vacuum. The junction displays a constant reverse saturation current respect the bias at high temperature, while at lower temperature the saturation current grows exponentially with the bias. This behaviour can be explained by taking into the account the graphene low density of states. The application of a negative (or positive) bias makes the graphene Fermi level shift up (or down) and thus it reduces (or increases) the Schottky barrier. This phenomenon is not visible at higher temperature since the charges possess higher energy and can easily overcome the barrier showing a constant reverse current. Also, the substrate geometry enhances this behaviour: The pillar corners magnify the electric field and induce a stronger potential on the graphene, thus modifying the Schottky barrier [32].

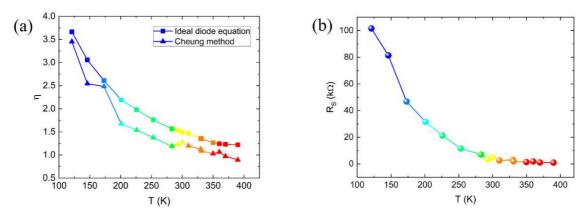

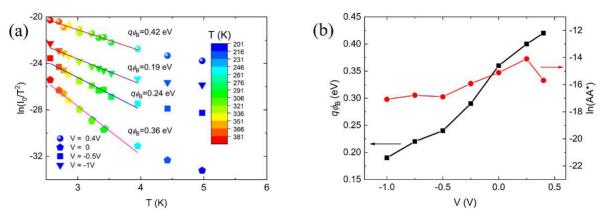

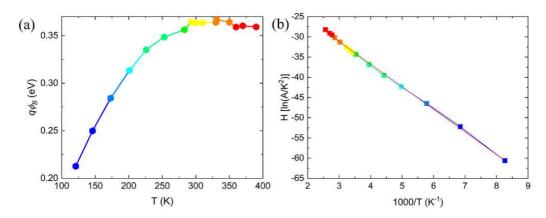

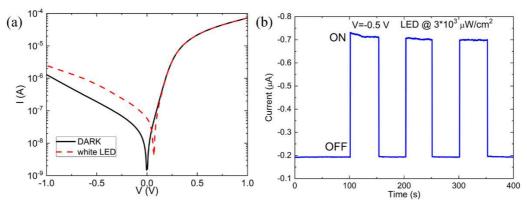

The second device was realized to confirm what we observed in the previous one. From a highly doped silicon substrate a matrix of  $\sim 500 \, nm$  height tips were patterned and then covered with a CVD grown oxide layer. The silicon tips were then subjected to CMP till revealing a circular surface with a diameter of  $50 \, nm$ . Finally, a commercial graphene monolayer was transferred on the top. The Gr/Si-tip I-V characteristics were measured at different temperature and in low vacuum. The Gr/Si-tip saturation current grows exponentially at each temperature. We determined the Schottky barrier at different bias and we observed a linear increase with respect to the bias. This result confirmed what we expected from the study of the graphene on Si pillars and suggested that more performant and high-quality Gr/Si junctions can be achieved by reducing the junction surface and by using a sharper geometry [28].

In summary, in this work, I fabricated and characterized different Gr/Si junctions and studied how the doping and the geometry of the substrate affects the I-V characteristics and Schottky barrier. I observed that a Gr/p-Si diode displays a low rectification and tends to degrade at higher temperature, while a Gr/n-Si diode shows a rectification of 4 order of magnitude and withstands higher temperatures. Both devices display a photocurrent almost higher than the forward current due to the MOS capacitor connected in parallel with the Gr/Si Schottky diode. This result is very interesting since both devices were not fabricated for photodetection and gives a clue on how to increase Gr/Si photo-sensitivity. We observed also that it is possible to tune the Schottky barrier height by patterning the substrate with a pillar or a tip geometry, which enable better control of the Schottky barrier height. The possibility to tune the Schottky barrier allows to detect different light wavelengths. These results could be the milestone to produce a new generation of cheaper tunable high sensible photodetectors.

## 1 Graphene

#### 1.1 Introduction

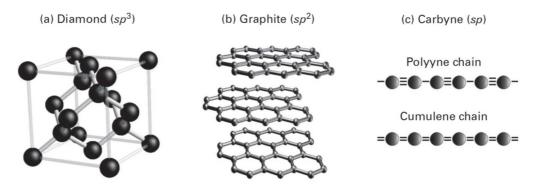

Carbon is one of the most versatile elements in nature, it can form different compounds by establishing different types of bonds. Carbon ground state electronic configuration is  $1s^22s^22p^2$  and possesses four valence electrons, 2s and 2p. Since two unpaired 2p electrons are present, Carbon tends to maximize the number of bonds by rearranging the configuration of the valence electrons. Such rearrangement is known as hybridization and only the 2s and 2p electrons are affected. One of the 2s electrons is promoted in the 2p orbital creating an excited state. Below, I will briefly describe the three hybridization possible configurations.

The 2s and 2p orbitals can mix in order to form three different hybrid orbitals. One possible hybridization consists in the formation of four  $sp^3$  orbitals each filled with one electron (Fig. 1 (a)). In order to reduce the repulsion between them, the hybrid orbitals arrange themselves in a tetrahedral geometry and form four  $\sigma$  bonds with an angle of 109.5° with the nearest carbon atoms. Carbon atoms in this configuration can be found in diamond and Methane  $(CH_4)$ .

Carbon's orbitals can also mix forming three  $sp^2$  hybrid orbital each filled with one electron (Fig. 2 (b)). These orbitals are arranged in a triangular planar shape with an angle of 120° and form three  $\sigma$  bonds with the nearest carbon atoms. The remaining p orbital is perpendicular to this plane and forms  $\pi$  bond by overlapping with the p orbital of another carbon atom outside of the plane. Ethylene  $(C_2H_4)$  and benzene  $(C_6H_6)$  are typical example of  $sp^2$  hybridization.

The last possible hybridization consists in the formation of two sp orbitals formed by the mixing of the 2s orbital and one of the 2p, each of them filled with one electron (Fig. 1 (c)). The geometry is linear with an angle of  $180^{\circ}$  between each orbital. The carbon atoms in this configuration are bound with the two nearest atoms by one  $\sigma$  bonds and the two  $\pi$  bonds formed by the two unmixed p orbitals.

Fig. 1 Carbon structure exhibiting different hybridization: (a) diamond  $(sp^3)$ ; (b) graphite  $(sp^2)$ ; and (c) carbine (sp).

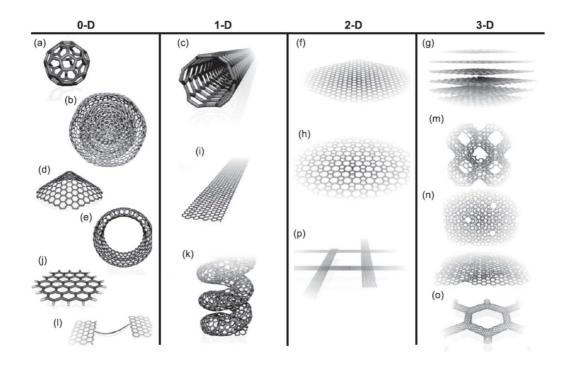

The  $sp^2$  hybridization is the one, which interests us the most. It exhibits a great variety of allotropes, from low-dimensional fullerenes, nanotubes and graphene nanoribbons, to two-

dimensional monolayer graphene, or stacked graphene multilayer. Of all of them, Fig. 2, graphene is the one on which the scientific community has been focused most of its attention in the last years because of its very interesting properties.

Graphene monolayers were first isolated in 2004 by Prof. Novoselov and Prof. Geim from bulk graphite by exfoliation (this technique is known as the "scotch tape method") [1], a discovery which was awarded with the Nobel Prize in 2010.

Fig. 2 Atomistic models of various sp²-like hybridized carbon nanostructures exhibiting different dimensionalities, 0D, 1D, 2D e 3D: (a) C60: buckminsterfullerene; (b) nested giant fullerenes or graphitic onions; (c) carbon nanotube; (d) nanocones or nanohors; (e) nanotorroids; (f) graphene surface; (g) 3D graphite crystal; (h) Haeckelite surface; (i) graphene nanoribbons; (j) graphene clusters; (k) helicoidal carbon nanotube; (l) short carbon chains; (m) 3D Schwarzite crystals; (n) carbon nanofoams (interconnected graphene surface with channels); (o) 3D nanotube network, and (p) nanoribbon 2D network

Graphene possesses higher electron mobility than silicon, higher electrical conductivity than the copper and a low optical coefficient [10,16,18,48]. All these properties make the graphene the perfect candidate to realize a new generation of faster electronic devices such as transistors [12,13,22–24], diodes [27–32,49], chemical-biological sensors [39–41], more sensitive photosensors, and cheaper solar panels [9,15,34–38].

In this chapter we will briefly describe the graphene electrical properties, from its band structure to its electrical conductivity. We will also focus on its optical properties and fabrication methods.

#### 1.2 Graphene electronics properties

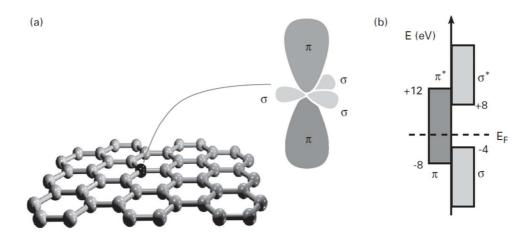

Graphene is a bidimensional material composed of carbon atoms arranged in a honeycomb lattice. This structure is characterized by two type of bonding within the  $sp^2$  hybridization,

the 2s,  $2p_x$  and  $2p_y$  combine to form the inplane  $\sigma$  and the  $\sigma^*$  orbital while the  $p_z$  orbital is perpendicular to the plane and forms with  $p_z$  neighbouring orbital  $\pi$  and  $\pi^*$  (Fig. 3 (a)). The  $\sigma$  bonds are strongly covalent bonds and are the ones responsible for the graphene mechanical properties. The difference in energies between them is greater than 12~eV so their contributions to the electrical properties can be disregarded (Fig. 3 (b)). Thus, the  $\pi$  orbitals are the only one responsible for the electronic properties.

Fig. 3 The carbon valence orbitals. (a) The three  $\sigma$  orbitals in graphene and the  $\pi$  orbital perpendicular to the sheet.

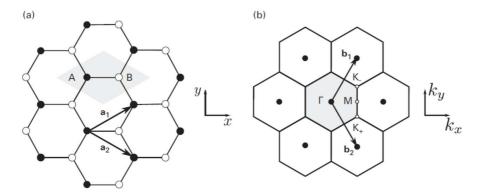

Graphene structure cannot be directly associated with a Bravais lattice. In order to determinate its electrical properties, we will consider the unit cell composed of two atoms. By doing so, we obtain a triangular Bravais lattice, Fig. 4 (a), whose basis vector are defined as

$$\vec{a}_1 = a\left(\frac{\sqrt{3}}{2}, \frac{1}{2}\right), \qquad \vec{a}_2 = a\left(\frac{\sqrt{3}}{2}, \frac{1}{2}\right)$$

(1.1)

where  $a = \sqrt{3}a_{cc}$  where  $a_{cc} = 1.42$  Å is the distance between two carbon atoms. By using the condition  $\vec{a}_i \cdot \vec{b}_j = 2\pi \delta_{ij}$  the reciprocal lattice vectors  $(\vec{b}_1, \vec{b}_2)$  can be obtained,

$$\vec{b}_1 = b\left(\frac{1}{2}, \frac{\sqrt{3}}{2}\right), \qquad \vec{b}_2 = b\left(\frac{1}{2}, \frac{\sqrt{3}}{2}\right),$$

(1.2)

with  $b = 4\pi/3a_{cc} = 4\pi/a\sqrt{3}$  (Fig. 4 (b)). The graphene reciprocal lattice is also a hexagonal lattice but is rotated by 90°. Two corners out of six are inequivalent, the other can be written as one of these two plus a reciprocal lattice vector. These points are denoted  $K_+$  and  $K_-$ :

$$\vec{K}_{+} = \frac{4\pi}{3a} \left( \frac{\sqrt{3}}{2}, \frac{1}{2} \right), \vec{K}_{-} = \frac{4\pi}{3a} \left( \frac{\sqrt{3}}{2}, \frac{1}{2} \right)$$

(1.3)

The dispersion relation  $E(\vec{k})$  is obtained from the tight-binding Hamiltonian

$$\mathcal{H}(\vec{k}) = \begin{pmatrix} 0 & -\gamma_0 (1 + \exp(i\vec{k} \cdot \vec{a}_1) + \exp(i\vec{k} \cdot \vec{a}_2)) \\ c. c. & 0 \end{pmatrix}. \tag{1.4}$$

where  $\gamma_0 \approx 2.7 eV$  is the nearest-neighbor hopping interaction between A and B sites and c. c. is the complex conjugate of the off-matrix element.

Fig. 4 Showing basis vector  $\vec{a}_1$  and  $\vec{a}_2$  in the hexagonal network of graphene. This network is a triangular Bravais lattice with a two tom-basis: A (full dots) and B (empty dots). (b) The reciprocal lattice points corresponding to the triangular Bravais lattice (full dots) as well as the associated basis vector  $\vec{b}_1$  and  $\vec{b}_2$ .

By diagonalizing  $\mathcal{H}(\vec{k})$  the energy relation is obtained:

$$E_{\pm}(\vec{k}) = \pm \gamma_0 |\alpha(\vec{k})|$$

$$= \pm \gamma_0 \sqrt{3 + 2\cos(\vec{k} \cdot \vec{a}_1) + 2\cos(\vec{k} \cdot \vec{a}_2) + 2\cos(\vec{k} \cdot (\vec{a}_2 - \vec{a}_1))}$$

(1.5)

Which can be further expanded:

$$E_{\pm}(k_x, k_y) = \pm \gamma_0 \sqrt{1 + 4\cos\left(\frac{\sqrt{3}k_x a}{2}\right)\cos\left(\frac{k_y a}{2}\right) + 4\cos^2\left(\frac{k_y a}{2}\right)}. \tag{1.6}$$

The wavevectors  $\vec{k} = (k_x, k_y)$  are chosen within the first hexagonal Brillouin zone. In the point  $\vec{K}_+$  and  $\vec{K}_-$ , the function  $\alpha(\vec{k}) = 0$  and corresponds to the point where the two bands meet with each other, Fig. 5. By expanding equation (1.6) for  $\vec{k}$  in the vicinity of  $K_+$  (or  $K_-$ ),  $\vec{k} = \vec{K}_+ + \vec{q}$  ( $\vec{k} = \vec{K}_- + \vec{q}$ ) a linear dispersion relation is obtained:

$$E_{\pm}(\vec{q}) = \pm \hbar \nu_F |\vec{q}| \tag{1.7}$$

where

$$\nu_F = \frac{\sqrt{3}\gamma_0 a}{2\hbar} \tag{1.8}$$

is the group velocity. Equation (1.7) states that the valence and the conduction band possess a conical shape the vertices of which meet at the Fermi level in six points, known as Dirac points, Fig. 5. Close to them, the electrons behave like massless Dirac fermions and their group velocity reaches the value of  $v_F \sim 8.5 \times 10^5 m/s$ .

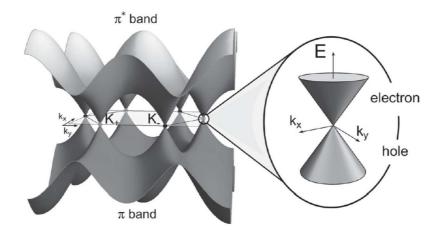

Fig. 5 Graphene  $\pi$  and  $\pi^*$  electronic bands. In this simple approach, the  $\pi$  and  $\pi^*$  bands are symmetric with respect to the valence bands. The linear dispersion relation close to  $K_+$  and  $K_-$  points of the first 2D Brillouin zone gives rise to the "Dirac cones" a shown on the right

#### 1.3 Graphene conductivity and mobility

The mobility and the conductivity in graphene depend on the microscopic scattering processes that occur in graphene at a given temperature [50–52]. For ideal and neutral graphene, the  $E_F$  is at Dirac point where  $n \approx 0$ . The position of the Fermi level above or below the Dirac point makes graphene a n- or p-doped semiconductor. In order to determinate the relation between the  $E_F$  and n, let us consider the number of states between q and q + dq, which is

$$N(q)dq = \frac{Aqdq}{2\pi} \cdot t \tag{1.9}$$

where A is the graphene surface where the number of states is calculated and t = 2 is the valley degeneracy. Using the dispersion relation equation (1.7):

$$N(q)dq = N(E)dE = Ag\frac{EdE}{\pi(\hbar\nu_E)^2}$$

(1.10)

by defining the density of states per energy and area g(E) = N(E)/A, we obtain

$$g(E) = \frac{2|E|}{\pi \hbar^2 v_E^2} = g_0|E| \tag{1.11}$$

and

$$n = \int_0^\infty g(E)f(E)dE = \frac{2}{\pi} \left(\frac{kT}{\hbar v_F}\right) F_1\left(\frac{E_F}{kT}\right) \approx \frac{1}{\pi} \left(\frac{E_F}{\hbar v_F}\right)^2 at T = 0K \quad (1.12)$$

where f(E) it is the Fermi function and  $F_1\left(\frac{E_F}{kT}\right)$  is the Fermi Dirac integral. Equation (1.12) states that the Fermi level changes as the square of the carrier density:

$$E_F = \mp \frac{h}{2\sqrt{\pi}} \nu_F \sqrt{n} \tag{1.13}$$

The (-) and (+) sign correspond to p- and n-type graphene respectively. It is also possible to shift the Fermi level using different chemicals, as we will see later.

Now that we know the relation between the  $E_F$  and n we can determinate the relation between the energy and the conductivity. Let us consider the case in which the  $E_F$  is away from the Dirac point and the carrier density is high. The presence of inhomogeneity or other disorder act as scattering point and reduce the electron mean free path length l. If L is the graphene length, we can distinguish two transport regimes. In the case l > L, the transport is ballistic, and the carriers travel from one side to the other of graphene at Fermi velocity  $\nu_F$ . In the other case, l < L, the carrier undergo elastic and anelastic collisions, this regime is known as diffusive. Both situation can be described using the Landauer formalism [53].

$$\sigma = \frac{L}{W} \frac{2e^2}{h} \int_0^\infty T(E) M(E) \left( -\frac{\partial f}{\partial E} \right) dE \tag{1.14}$$

where W is the width of the graphene, T(E) is the transmission function which value depend on the transport regime, and M(E) is the number of conduction channels. For ballistic transport

$$T(E) = 1 \tag{1.15}$$

while for diffusive:

$$T(E) = \frac{\lambda(E)}{\lambda(E) + L} \tag{1.16}$$

M(E) can be calculated [54] from the dispersion relation equation (1.7)

$$M(E) = W \frac{2|E|}{\pi \hbar \nu_F}. (1.17)$$

Equation (1.17) present a linear relation with the energy. From equations (1.14)-(1.17), under the approximation that  $-\frac{\partial f}{\partial E} \approx \delta(E - E_F)$  valid for  $T \to 0K$ , we obtain

$$\sigma = \frac{2e^2}{h} \left( \frac{2E_F}{\pi \hbar \nu_F} \right) \lambda(E_F). \tag{1.18}$$

In the ballistic regime  $\lambda = L$ , while for diffusive regime

$$\lambda(E) = \frac{\pi}{2} \nu_F \tau(E) \tag{1.19}$$

where  $\tau$  is the momentum relaxation time.

Now, we can introduce the mobility  $\mu$  defined for bidimensional materials as:

$$\mu = \frac{\sigma}{en} \qquad \left[ \frac{V}{cm^2 \, s} \right] \tag{1.20}$$

which is valid for both diffusive and ballistic regime. From the definition, the  $\mu$  is also affected by the scattering process that occurs in graphene at a given temperature [50–52].

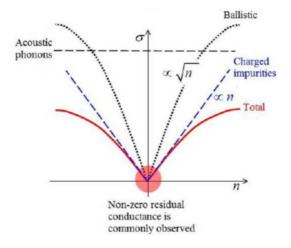

In the ballistic regime  $\sigma \propto \sqrt{n}$  (Fig. 6) and  $\mu \propto 1/\sqrt{n}$ . This dependence has been experimentally observed [55]. Experimental value of  $\mu$  as high as  $2 \times 10^5 cm^2 V^{-1} s^{-1}$  for  $n < 5 \times 10^9 cm^{-2}$  have been measured on suspended graphene at liquid helium temperature [56–61]. While on SiO<sub>2</sub> substrate, where the transport is diffusive, a value of  $\mu \approx 10 \div 15 \times 10^3 cm^2 V^{-1} s^{-1}$  have been measured [58].

In the diffusive regime  $\lambda(E)$  and  $\tau(E)$  depend on the scattering mechanisms, which are three in the graphene: Coulomb scattering due to charged impurities, defects and adsorbates, and electron-phonon scattering.

Charge impurity scattering is due to the presence of ions on the graphene surface or on the top of the dielectric. Its effects are more relevant at low energies and the relaxation time corresponding to it varies linearly with energy,  $\tau(E) \propto E$ , [59,61]. From equations (1.20), (1.13), (1.18) and (1.19) we can observe that there is a linear relation between  $\sigma$  and n (Fig. 6), and  $\mu$  is independent of n. The Coulomb scattering is mainly due to the charge trapping so its effect can be reduced by using dielectric less prone to trap charge such as BN [60]. Another possible solution is to remove the ions by annealing the sample at high temperature [62].

The short range scattering is due to the presence of inhomogeneities in the graphene lattice such as localized defect, vacancies and crack [48,63]. Its potential can be approximated using a delta function. The resulting scattering rate is proportional to the final density state, so  $1/\tau(E) \propto E$  and it is temperature independent. In this case the conductivity  $\sigma$  does not depend on n and  $\mu \propto 1/n$ .

Fig. 6 Conductivity vs carrier density for graphene

The electron-phonon scattering can be considered an intrinsic scattering source and is temperature dependent, so it is present even if there are no imperfections. The scattering of longitudinal acoustic phonons and electrons can be considered quasi-elastic since the phonon energies are negligible respect the electrons Fermi energy [62–64]. Optical phonons can also scatter carriers, especially at temperature above 300K and are believed to be responsible

for the decrease in conductivity at high temperature [65]. The total graphene conductivity  $\sigma$  will be equal to

$$\frac{1}{\sigma_{Tot}} = \frac{1}{\sigma_1} + \frac{1}{\sigma_2} + \cdots, \tag{1.21}$$

where  $\sigma_i$  is the conductivity corresponding to a given scattering process.

#### 1.4 Graphene Doping

Graphene can be doped by a chemical approach, using two different methods.

#### 1.4.1 Substitutional doping

This method consists of the introduction of different atoms in the graphene lattice during the fabrication process and offers a good and stable doping.

Typically, acceptor-like boron and donor-like nitrogen can dope graphene as p-type and n-type respectively. The substitution of a graphene atom with a nitrogen one is achieved introducing N-contained precursor gas such as  $NH_3$ ,  $CH_3CN$ , and  $C_5H_5N$ , accompanied by the carbon source in the CVD growth process. Similar results can be achieved by post-growth treatments, such as plasma treatment in N-contained gas. While p-doped graphene can be realized using arch discharge with graphite electrode in the presence of  $H_2 + B_2H_6$  or using boron stuffed graphite electrodes. N-doped graphene exhibits a lower carrier mobility but larger on/off ratio than that intrinsic graphene [66,67]. Other elements such as phosphorous, [68] silicon[69] and sulfur[70] can also dope the graphene.

#### 1.4.2 Surface doping

Another method for doping graphene has been achieved by adsorbing inorganic or organic molecules on its surface. This method is not the most efficient, it does not disrupt strongly the electronic structure and its effect will weaken or disappear if these molecules desorb from graphene. Substance such as  $H_2O_2$ ,  $NO_2$ ,  $Br_2$ ,  $I_2$  and tetrafluorotetracyanoquinodimethane ( $F_4 - TNCNQ$ ) are strong electron acceptor and can p-dope graphene [71–73]. Also, PMMA residue can p-doped the graphene[74]. While n-doped graphene can be obtained using  $NH_3$ , ethanol, and poly(ethylene imine) (PEI) [75,76]. Graphene can be also doped via hydrogenation, fluorination or chlorination with covalent C-H, C-F or C-Cl bond trough plasma reaction or photochemical process [77,78]. Or by the substrate or metal electrode [79–81], Au and Pt cause p-doping, while Al, Ag, and Cu induce n-doping.

#### 1.4.3 Electrical doping

The graphene  $E_F$  can be also shifted by the application of a potential through a gate electrode. Graphene field effect devices (GFETs) operate based on this phenomenon to.

## 1.5 Optical properties

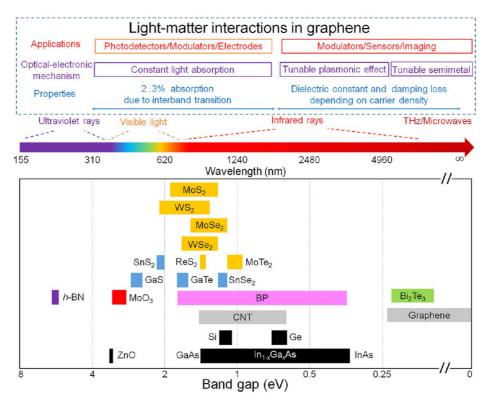

Graphene possesses also very interesting optical properties thanks to its unique band structure. It is able to absorb light on a broad spectrum ranging from ultraviolet and visible to infrared and terahertz (THz) region.

Fig. 7 Electromagnetic spectrum from ultraviolet rays to THz/microwaves and the corresponding lightmatter interactions in graphene and the bandgap values for different 2D and conventional semiconductor [18]

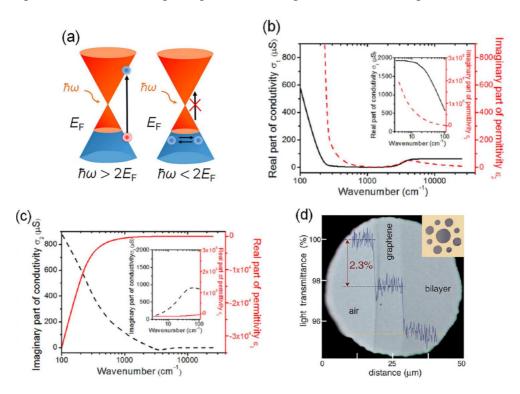

When a photon with energy  $\hbar\omega$  hit the graphene electron, two photoexcitation mechanisms occur: interband transition and intraband transitions [82,83]. When an electron in the valence band is hit by a photon with energy  $\hbar\omega > 2E_F$ , it acquires enough energy to jump from the valence to the conduction band leaving behind a hole. This phenomenon is known as interband transition. If the energy  $\hbar\omega < 2E_F$ , the electron does not possess enough energy to jump and intraband transition occurs (Fig. 7a) .The light-graphene interaction can be described in terms of complex dynamical conductivity  $\sigma = \sigma_{inter} + \sigma_{intra}$ . Using the random phase approximation (RPA),[83–85] we obtain

$$\sigma = \frac{e^2}{4\hbar} \left[ \theta \left( \omega - \frac{2E_F}{\hbar} \right) - \frac{i}{2\pi} \ln \left( \frac{\omega + 2E_F/\hbar}{\omega - 2E_F/\hbar} \right)^2 \right] + \frac{ie^2 k_B T}{\pi \hbar (\omega + i\tau^{-1})} \left[ \frac{E_F}{k_B T} + 2 \ln \left( \exp \left( -\frac{E_F}{k_B T} \right) + 1 \right) \right].$$

(1.22)

The first term represents the conductivity due to the interband transition. The step function  $\theta(\omega)$  conveys the condition for a photon exciting an electron from the valence band to the conduction band. The second term represents the intraband transition described by the free electron model or Drude model. For the Fermi-Dirac statistic, if  $E_F \gg k_B T$ , the intraband conductivity becomes:

$$\sigma_{intra} = \frac{ie^2|E_F|}{\pi\hbar(\omega + i\tau^{-1})}.$$

(1.23)

Once the conductivity is determinated, the permittivity of graphene can be calculated from  $\varepsilon = i\sigma/\omega$ , as well the refraction index  $n_i = \sqrt{\varepsilon}$ . The dynamic conductivity measured in the wavelength from the visible light region to THz region is shown in Fig. 8 b) and c).

Fig. 8 (a) Interband (left) and intraband (right) transition in graphene. The real part(b) and the imaginary part (c) of conductivity (black line) and corresponding imaginary part (b) and real (c) of permittivity (blue dash line) from visible to far infrared region for graphene; the inset is the THz region. (d) Looking through one-atom-thick crystals. (A) Photograph of a 50-mm aperture partially covered by graphene and its bilayer. The line scan profile shows the intensity of transmitted white light along the yellow line. (Inset) [86]

Let's consider the case the graphene is illuminated by photon with energy  $\hbar\omega > 2E_F$  (from visible to near infrared light), the dynamical conductivity (1.22) is dominated by loss (real part) due to the interband transition and the real part of the first term becomes  $e^2/4\hbar$ . We obtain a constant light absorption of 2.3%, Fig. 8 d). In the lower frequency region, such as infrared and THz region, the dynamical conductivity is dominated by the intraband transition. In this case, the graphene responds to light depend on the scattering rate  $\tau^{-1}$  and the frequency  $\omega$ . In the case  $\omega > \tau^{-1}$ , the imaginary part of the conductivity dominates, and the graphene exhibits a negative permittivity with ohmic losses, and  $\varepsilon = i\sigma/\omega$ . If  $\omega \ll \tau^{-1}$ , the real part of conductivity is much larger than the imaginary part. In this case graphene exhibits a metal reflection due to the high conductivity in the THz to microwave region [87,88].

## 1.6 Graphene Synthesis

Graphene can be fabricated using different methods: 1) micro-mechanical exfoliation of highly ordered pyrolytic graphite, 2) chemical vapour deposition (CVD), 3) epitaxial growth on Silicon Carbide (SiC), and 4) reduction of graphene oxide (GO).

The micro-mechanical exfoliation of highly ordered pyrolytic graphite (HOPG) was first introduced by Prof. Geim and Prof. Novoselov in 2004 [1]. The method is very simple, flakes of HOPG are repeatedly peeled using scotch tape until fading layers of graphite are left on the tape. The flakes are then transferred by pressing the scotch tape onto a substrate, typically Si or SiO<sub>2</sub>.

The CVD fabrication method uses a mixture of methane (or any other hydrocarbon) and hydrogen in argon under low pressure and use a metal as a catalyst and substrate to grow graphene [89]. The growth of the graphene takes place at the temperature of  $\sim 1000\,^{\circ}C$ . At this temperature, the composition of the carbon containing gas on the metal surface creates a concentration gradient between the surface and the bulk, causing carbon atoms to diffuse into the metal and form a solid solution. Upon cooling, carbon atoms dissolved in the metal at high temperature precipitate out and segregate at the metal surface, forming one or more graphene layer. Metal such as Cu, Ni, Ru, Ir are the most used one. After a thin layer of poly(methyl methacrylate) (PMMA) is spin coated on it.

Graphene layers can be epitaxially formed by heating silicon carbide (SiC) in ultra-high vacuum to temperature between 1000°C and 1500°C [90,91]. Hexagonal 4H-SiC and 6H-SiC polytypes are commonly employed. The high temperature causes Si to sublimate and leaves behind a carbon rich surface which is graphitic in nature and can be used to form graphene.

The reduction of the GO allows to obtain graphene from raw graphite. This method is cheaper than the other shown before due to the low cost of the material and the chemicals. Further details can be found in [92–94].

All these methods have pros and cons. The micro-mechanical exfoliation method allows to fabricate high-quality graphene, but the films size is tens of micrometres and is not scalable[95]. By reducing the GO is possible to fabricate large quantities of flakes that can be stack together to form larger flakes, but the electrical properties are worse than the flakes obtained from micro-mechanical exfoliation [96]. Graphene epitaxially growth from SiC possesses a good charge mobility and electrical conductivity, but the layer surface is limited by the size of high-quality SiC substrates [97]. The CVD fabrication method can be used to grow large high quality graphene with high electrical conductivity and high charge mobility on transition metal, usually copper [98,99]. The pros of the CVD fabrication methods are the compatibility with the integrated circuit fabrication process [8], the low cost and the efficiency. The cons are the formation of cracks and the presence of chemical residue due to the etching and the transfer process [100,101] which can alter the graphene electronic properties.

### 1.7 Graphene Wet Transfer Process

Graphene obtained from the scotch tape method can be easily transfer by pressing the scotch tape with the flakes on the substrate. As we explained before this method allow to obtain high-quality graphene but is not possible to control the flakes dimension. The CVD fabrication method has been considered as the best solution to produce large area high-quality graphene layers. The result of this process is a structure composed by the substrate

(in this case we will consider copper foil), a graphene monolayer and the PMMA layer. The PMMA layer has the function to protect and to sustain the graphene layer.

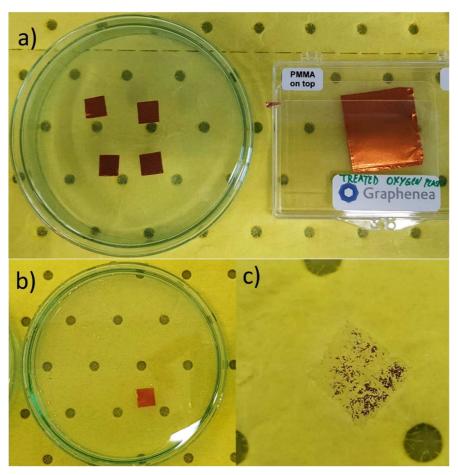

In the following, we will describe a typical wet transfer process using commercial graphene from Graphenea®. Starting from a PMMA/graphene/Cu sample, squares with similar size are cut and place between two Petri plate in order to reduce the wrinkles (Fig. 9 (a)). Cu is etched using a solution of  $2 \div 3$  gr of ammonium persulfate (APS) and 50 ml of deionized water (DI). The PMMA/graphene/Cu sandwich is placed on the solution with the PMMA on top (Fig. 9 (b)) and it is left rest until the Cu is complete etched.

Fig. 9 (a) Commercial Cu/graphene/PMMA stack cuttend in four pieces. (b) Cu/graphene/PMMA stack floating on the APS and DI solution. (c) graphene/PMMA after one hour in the etching solution, trace of the Cu foil are visible.

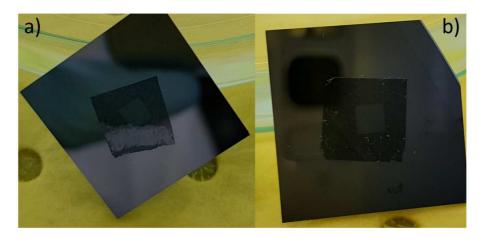

The PMMA/graphene is fished using a microscope slide, it is put into another Petri plate filled with DI and washed. This step can be repeated many times to ensure the complete removal of Cu traces. At this point the PMMA/graphene is fished using the desired substrate and left to dry (Fig. 10 (a)). When it has dried completely (Fig. 10 (b)), the PMMA top layer is removed with an acetone bath and isopropanol.

Fig. 10 (a) Graphene/PMMA stack deposited on  $Si/SiO_2$ , the substrate is inclined to favour the water evaporation. The water under the graphene tend to accumulate on the bottom. (b) Photo of a dried sample.

#### 2 Schottky Junction

In the previous chapter, we described the graphene structure and its electronic properties. We observed that graphene possesses a bandgap-less structure which make it a semimetal. As we will explain in chapter 3, graphene/silicon heterojunction behaves as a metal/semiconductor Schottky diode. For this reason, we will briefly discuss here the physical phenomena in this type of junction. This chapter content are a sunt of what it is already widely known and described in the reference [102–104].

#### 2.1 Equilibrium in electronic system

All electronic devices communicate through metal/semiconductor contact. The properties of these contacts can vary considerably, and it is necessary to consider several factors in order to understand them. We will start by considering in general the nature of the thermal equilibrium that is established when a metal and a semiconductor are in intimate contact. Application of the equilibrium principles to metals and semiconductors provides a simple theory of ohmic and rectifying behaviour in various metal semiconductor system. This theory does not fully describe the system, we have also to consider effect due to the nature of solid interfaces.

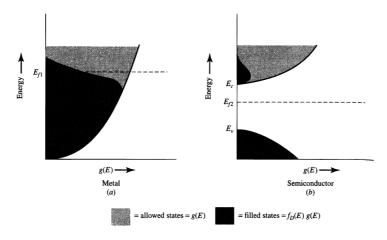

Let us consider the band structure of a metal (m) and a semiconductor (s). When the two system are separate and do not interact with each other, both the systems of electronic states and their Fermi level are independent. Each system has a density of allowed states N(E) per unit energy, part of them are occupied n(E) while the other are empty v(E). These quantities are related by the Fermi-Dirac distribution function:

$$f_{m,s} = \frac{1}{1 + \exp\left(\frac{E - E_{fm,s}}{kT}\right)}$$

(2.1)

where  $E_{fm,s}$  are the Fermi level of the metal and the semiconductor. The filled state density is obtained from the relation:

$$n_{m,s} = g_{m,s} \times f_{m,s} \tag{2.2}$$

where g(E) is the density of allowed states per unit energy, while the vacant from:

$$v_{m,s} = g_{m,s} \times (1 - f_{m,s}) \tag{2.3}$$

Let us bring the two system into intimate contact, they begin to interact. The electrons flow from one to the other until the equilibrium is reached and there is no exchange of charge. This does not mean the cession of all process, rather it means that every process and its inverse are occurring at the same rate. Equilibrium can be expressed mathematically by considering that the transfer probability is proportional to the population of the electrons  $n(E_x)$  available to transfer at given energy  $E_x$  and also proportional to the density of the available states  $v(E_x)$  to which the electron can transfer. Therefore, at thermal equilibrium:

$$n_m \times v_s = n_s \times v_m \tag{2.4}$$

at any given energy.

Using equations (2.2) and (2.3) in equation (2.4), we have

$$f_m g_m g_s = f_s g_s g_m \tag{2.5}$$

Equation (2.5) can only be true if  $f_m = f_s$  or, by equation (2.1), if  $E_{f1} = E_{f2}$ . This means any two system are in thermal equilibrium when they have the same Fermi energy.

#### 2.2 Ideal Metal-Semiconductor Junction

Let's consider the band structure of a metal and a n-doped semiconductor which do not interact with each other, Fig. 11. In the metal, the Fermi level is immersed within a continuum of allowed states, while in a semiconductor, under usual circumstance, the density of the states is negligible at the Fermi level.

Fig. 11 a) Allowed electronic energy states g(e) in an ideal metal and b) in a semiconductor.

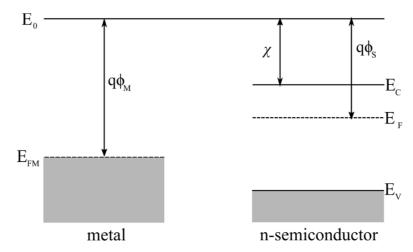

For our discussion we will consider the general schematic view of Fig. 12.  $E_0$  is the energy an electron would have if it were free from any influence of the material and it is called vacuum or free-electron energy.  $q\phi$  is the workfunction of the material and it is equal to the difference between  $E_0$  and  $E_f$ .  $E_c$  and  $E_v$  are the conduction and the valence band. The difference of the  $E_c$  and  $E_v$  is the band gap. The semiconductor Fermi level reside in the bandgap and it can be shift by doping the semiconductor. The difference between the vacuum level and the  $E_c$  is the electron affinity  $(q\chi)$  and it is a constant of the material.

Fig. 12 Energy level of an ideal metal and a n-doped semiconductor.

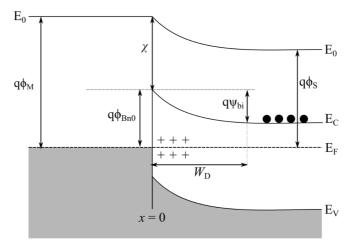

Let us consider the case the  $q\phi_m > q\phi_s$  and the semiconductor is n-doped. When the two system are brought together, they begin to interact with each other as we described before until they reached the thermal equilibrium and the Fermi level is constant for both of them, Fig. 13.

Fig. 13 Idealized equilibrium band diagram for a metal-semiconductor rectifying contact.

Now, we can define the Schottky barrier as the difference of the  $q\phi_M$  and the  $\chi$

$$q\phi_{Rn0} = q(\phi_M - \gamma) \tag{2.6}$$

$W_D$  is the depletion layer and  $q\psi_{bi}$  is the built-in potential which we will discuss later. Conversely, in the case the semiconductor is p-doped, the Schottky barrier will be

$$q\phi_{Bp0} = E_g - q(\phi_M - \chi). \tag{2.7}$$

When the junction is formed, electrons flow from the semiconductor to the metal surface leaving behind a region of positive ion. This region is known as depletion layer  $W_D$ . This

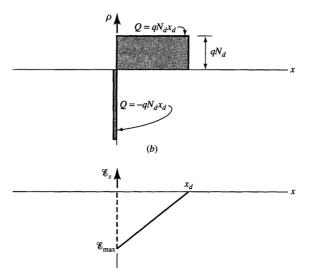

distribution will form an electric field which prevent further charge exchange. The charge and electric field diagram are plotted in Fig. 14.

Fig. 14 Charge at idealized metal-semiconductor junction.

Before we determinate the electric field ( $\mathcal{E}$ ) and  $W_D$ , let's assume that the charge density  $\rho \approx qN_D$ , where  $N_D$  is the doping concentration, for  $x < W_D$  and the  $\mathcal{E} \approx 0$  and  $\rho \approx 0$  for  $x > W_D$ . We obtain

$$W_D = \sqrt{\frac{2\varepsilon_S}{qN_D} \left(\psi_{bi} - V - \frac{kT}{q}\right)}$$

(2.8)

$$|\mathcal{E}(x)| = \frac{qN_D}{\varepsilon_S}(W_D - x) = \mathcal{E}_m - \frac{qN_Dx}{\varepsilon_S}$$

(2.9)

$$E_C(x) = q\phi_{B0} - \frac{q^2 N_D}{\varepsilon_S} \left( W_d x - \frac{x^2}{2} \right) \tag{2.10}$$

Where the term kT/q arise from the contribution of the majority of carrier distribution tail and  $\mathcal{E}_m$  is maximum electric field strength which occurs at x = 0:

$$\mathcal{E}_m = \mathcal{E}(x=0) = \sqrt{\frac{2qN_D}{\varepsilon_S} \left(\psi_{bi} - V - \frac{kT}{q}\right)} = \frac{2\left[\psi_{bi} - V - \left(\frac{kT}{q}\right)\right]}{W_D}.$$

(2.11)

The space charge  $Q_{SC}$  per unit of area of the semiconductor and the depletion layer capacitance  $C_d$  per unit area are given by

$$Q_{SC} = qN_DW_D = \sqrt{2q\varepsilon_S N_D \left(\psi_{bi} - V - \frac{kT}{q}\right)}$$

(2.12)

$$C_D = \frac{\varepsilon_S}{W_D} = \sqrt{\frac{q \varepsilon_S N_D}{2 \left[ \psi_{bi} - V - \frac{kT}{q} \right]}}.$$

(2.13)

Eq.(2.13) can be written in the form

$$\frac{1}{C_D^2} = \frac{2\left[\psi_{bi} - V - \frac{kT}{q}\right]}{q\varepsilon_S N_D} \tag{2.14}$$

or

$$N_D = \frac{2}{q\varepsilon_S} \left( -\frac{1}{d(1/C_D^2)/dV} \right). \tag{2.15}$$

If  $N_D$  is constant through the depletion region, a straight line is obtained by plotting  $1/C_D^2$  versus the voltage. If  $N_D$  is not a constant, the differential capacitance method can be used to determinate the doping profile from eq.(2.15).

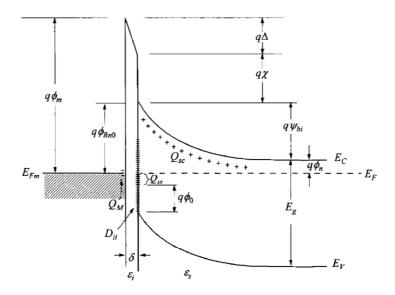

#### 2.3 Interface states

In the previous section, we defined the Schottky barrier as the difference between the metal work function and the electron affinity, but we did not consider the effect induced by the interface states.

A detailed energy band diagram of a metal and a n-doped semiconductor is showed in Fig. 15. As we can see there are different energy level and interface trap which can affect the junction. The first one we are going to consider is the energy level  $q\phi_0$  above the  $E_V$  at the surface. It is called the neutral level and above it the states are of acceptor type (neutral when empty and negative when occupied) and below the states are of donor type (neutral when full of electrons, positively charged when empty). The presence of these traps can affect the Schottky barrier height.

Let's consider the case of a semiconductor with acceptor interface trap whose density is  $D_{it}$  states/cm<sup>2</sup>·eV and let's suppose it is constant over the energy range from  $q\phi_0 + E_V$  to the Fermi level. The interface-trap charge density on the semiconductor  $Q_{SS}$  is therefore negative and is given by

$$Q_{SS} = -qD_{it}(E_g - q\phi_0 - q\phi_{Bn0}) \frac{C}{cm^2}.$$

(2.16)

The space charge that forms in the depletion layer of the semiconductor at thermal equilibrium is given as

$$Q_{SC} = qN_DW_D = \sqrt{2q\varepsilon_S N_D \left(\phi_{Bn0} - \phi_n - \frac{kT}{q}\right)}.$$

(2.17)

The sum of (2.16) and (2.17) is equal to the total of the surface charge density on the semiconductor surface. In the absence of any space-charge effects in the interfacial layer, an

exactly equal and opposite charge,  $Q_M$  ( $C/cm^2$ ), develops on the metal surface. For thin interfacial layers such space-charge effects are negligible and  $Q_M$  can be written as

$$Q_M = -(Q_{SS} + Q_{SC}) (2.18)$$

The potential  $\Delta$  across the interfacial layer can be obtained by applying the Gauss' law:

$$\Delta = -\frac{\delta Q_M}{\varepsilon_i} \tag{2.19}$$

where  $\varepsilon_i$  is the permittivity of the interfacial layer and  $\delta$  is the thickness. The potential  $\Delta$  can be also obtained by considering the potentials:

$$\Delta = \phi_m - (\chi + \phi_{Bn0}) \tag{2.20}$$

The potential  $\Delta$  can be exploited to determinate the relation between the charge densities  $Q_{SS}$  and  $Q_{SC}$  and the energy-band diagram:

$$\phi_{m} - \chi - \phi_{Bn}$$

$$= \sqrt{\frac{2q\varepsilon_{S}N_{D}\delta^{2}}{\varepsilon_{i}^{2}}} \left(\phi_{Bn} - \phi_{n} - \frac{kt}{q}\right)$$

$$-\frac{qD_{it}\delta}{\varepsilon_{i}} \left(E_{g} - q\phi_{0} - q\phi_{Bn}\right). \tag{2.21}$$

Let's introduce the quantities

$$c_1 \equiv \frac{2q\varepsilon_S N_D \delta^2}{\varepsilon_i^2} \tag{2.22}$$

$$c_2 \equiv \frac{\varepsilon_i}{\varepsilon_i + q^2 \delta D_{it}} \tag{2.23}$$

which contain all the interfacial properties.  $c_1$  can be calculate from equation (2.22) if values of  $\delta$  and  $\varepsilon_i$  are estimated.

$\phi_m$  = Work function of metal

$\phi_{Bn0}$  = Barrier height (without image-force lowering)

$\phi_0$  = Neutral level (above  $E_{\nu}$ ) of interface states

$\Delta$  = Potential across interfacial layer

χ = Electron affinity of semiconductor

$\psi_{bi}$  = Built-in potential

$\delta$  = Thickness of interfacial layer

$Q_{sc}$  = Space-charge density in semiconductor

$Q_{ss}$  = Interface-trap charge

$Q_M$  = Surface-charge density on metal

$D_{it}$  = Interface-trap density

$\varepsilon_i$  = Permittivity of interfacial layer (vacuum)

$\varepsilon_s$  = Permittivity of semiconductor

Fig. 15 Detailed energy band diagram of a metal and n-doped semiconductor with an interfacial layer of the order of atomic distance.

There are two limiting cases which can be obtained directly equation(2.21):

1. When  $D_{it} \rightarrow \infty$ , then  $c_2 \rightarrow 0$  and

$$q\phi_{Bn0} = E_a - q\phi_0 \tag{2.24}$$

The Fermi level is pinned by the surface states at the value  $q\phi_0$  above the valence band. The barrier height is independent of the metal workfunction and is determinated entirely by the surface properties of the semiconductor.

2. When  $D_{it} \rightarrow 0$ , and  $c_2 \rightarrow 1$  and

$$q\phi_{Bn0} = q(\phi_m - \chi) \tag{2.25}$$

which is the definition of the Schottky barrier when the surface state effects are neglected.

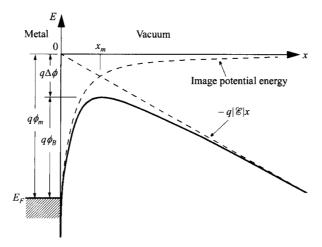

## 2.4 Image force lowering

Let us consider a metal and n-doped semiconductor junction. As described before, at thermal equilibrium, negative charges will accumulate on the metal surface, while positive charge

will distribute in the semiconductor depletion layer. The force of attraction between the electron and the induced positive charge is equivalent to the force that would exist between the electron and an equal positive charge at -x. We will refer to the positive charge as the image charge. The force between the charge and the image charge, known as image force, is

$$F = -\frac{q^2}{4\pi\varepsilon_S(2x)^2} = -\frac{q^2}{16\pi\varepsilon_S x^2}$$

(2.26)

The work done to an electron in the course of its transfer from infinity to the point x is given by

$$E(x) = \int_{\infty}^{x} F dx = -\frac{q^2}{16\pi\varepsilon_S x}.$$

(2.27)

Fig. 16 Energy band diagram of the metal-semiconductor junction considering the Schottky barrier lowering effect.

When an external electric field  $\mathcal{E}$  is applied, the electron potential energy  $(E_{PE})$  is

$$E_{PE} = -\frac{q^2}{16\pi\varepsilon_{\rm S}x} - q\mathcal{E}x. \tag{2.28}$$

The  $E_{PE}$  affects the Schottky barrier height reducing it of a quantity  $\Delta \phi$  in the point where it is maximum  $x_m$ , Fig. 16.  $x_m$  and  $\Delta \phi$  are given by the conditions  $d(E_{PE})/dx$ :

$$x_m = \sqrt{\frac{q}{16\pi\varepsilon_S|\mathcal{E}|}}. (2.29)$$

$$\Delta \phi = \sqrt{\frac{q|\mathcal{E}|}{4\pi\varepsilon_S}} = 2|\mathcal{E}|x_m. \tag{2.30}$$

In the Schottky diode, the electric field is not constant with the distance, and the maximum value at the surface based on the depletion approximation can be used,

$$\mathcal{E}_m = \sqrt{\frac{2qN_D|\psi_S|}{\varepsilon_S}},\tag{2.31}$$

$\psi_S$  is the surface potential:

$$\psi_S = \phi_{Bn0} - \phi_n + V_R. \tag{2.32}$$

where  $V_R$  is the reverse bias. Substituting (2.31) in (2.30) we obtain

$$\Delta \phi = \sqrt{\frac{q\mathcal{E}_m}{4\pi\varepsilon_S}} = \left[\frac{q^3 N_D |\psi_S|}{8\pi^2 \varepsilon_S^3}\right]^{\frac{1}{4}}$$

(2.33)

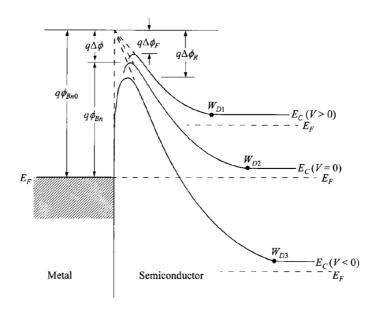

So, the application of a bias can reduce (reverse bias) or increase (forward bias) the Schottky barrier, Fig. 17, but its effect are related to the doping concentration  $N_D$ . The higher the  $N_D$ , greater will be the lowering Schottky barrier effect.

Fig. 17 Energy band diagram of the metal-semiconductor junction at different bias.

#### 2.5 Current voltage characteristic

The current transport in the Schottky diode is mainly due to majority carriers, that is electron for the n-type and holes for the p-type. There are five current transport processes which happen in a metal/semiconductor junction: (1) emission of the electrons from the semiconductor over the potential barrier into the metal, which is the dominant one for moderately doped semiconductor ( $N_D < 10^{17} cm^{-3}$ ), (2) quantum-mechanical tunneling of the electron trough the barrier (heavy doped semiconductor), (3) recombination in the space-charge region (which is similar the one happening in the p-n junction), (4) diffusion of the electrons in the depletion region, and (5) holes injected from the metal that diffuse into the semiconductor.

In this work we will only focus on the thermionic emission model and tunneling current.

#### 2.5.1 Thermionic Emission Current

The thermionic emission theory is derived from the assumption that the barrier height  $q\phi_{Bn} \gg kT$ , the thermal equilibrium is established at the junction and the current due to the exchange of charges from the semiconductor to the metal is balanced by the one from the metal to the semiconductor. These currents are proportional to the density of electrons at the boundary. At equilibrium, the density n is

$$n = \int_0^\infty f(E)g(E)dE \tag{2.34}$$

where g(E) is the density of allowed states per volume and energy in the semiconductor, and f(E) is the Fermi-Dirac distributions we introduced before. In the semiconductor

$$g(E) = \frac{4\pi}{h^3} (2m_e^*)^{\frac{3}{2}} \sqrt{E - E_C} \quad for E > E_C$$

(2.35)

where h is the Planck constant and  $m_e^*$  is the electron effective mass. The current density from the metal to the semiconductor  $J_{M\to S}$  is given by the concentration of electrons with energies enough to overcome the potential barrier and traversing in the x-direction

$$J_{M\to S} = \int_{E_{Fn} + q\phi_{Bn}}^{\infty} q v_x dn \tag{2.36}$$

From equations (2.34) and (2.35),

$$dn = g(E)F(E)dE \approx \frac{4\pi(2m_e^*)^{\frac{3}{2}}}{h^3}\sqrt{E - E_C} \exp\left(-\frac{E - E_C + q\phi_n}{kT}\right)dE$$

(2.37)

Assuming that the electron energy in the conduction band is kinetic energy

$$E - E_C = \frac{1}{2} m_e^* v^2 \tag{2.38}$$

$$dE = m_e^* v dv (2.39)$$

$$\sqrt{E - E_C} = v \sqrt{\frac{m_e^*}{2}}. (2.40)$$

By substituting in equation (2.37), we obtain

$$dn \approx 2\left(\frac{m_e^*}{h}\right)^3 \exp\left(-\frac{q\phi_n}{kT}\right) \exp\left(-\frac{m_e^*v^2}{2kT}\right) (4\pi v^2 dv).$$

(2.41)

where

$$v^2 = v_x + v_y + v_z. (2.42)$$

Equation (2.41) is the number of electrons per unit volume that have velocities between v and v + dv, distributed over all directions. Since we are considering only the electrons which moves in x-direction, from equation (2.36), we obtain

$$J_{M\to S} = \left(\frac{4\pi q m_e^* k^2}{h^3}\right) T^2 \exp\left(-\frac{q\phi_n}{kT}\right) \exp\left(-\frac{m_e^* v_{0x}^2}{2kT}\right). \tag{2.43}$$

$v_{0x}$  is the minimum velocity required to surmount the barrier and is

$$\frac{1}{2}m_e^*v_{0x}^2 = q(\psi_{bi} - V). (2.44)$$

Substituting in equation (2.43)

$$J_{M\to S} = \left(\frac{4\pi q m_e^* k^2}{h^3}\right) T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right) \exp\left(\frac{qV}{kT}\right)$$

$$= A^* T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right) \exp\left(\frac{qV}{kT}\right), \tag{2.45}$$

and

$$A^* = \frac{4\pi q m_e^* k^2}{h^3} \tag{2.46}$$

is the Richardson constant for thermionic emission, neglecting the effects of optical-phonon scattering and quantum mechanical reflection. For free electrons ( $m_e^* = m_0$ ) the Richardson constant is  $120 \, A/cm^2 K^2$ . Although the Richardson constant depends on the material properties of the semiconductor, it has been demonstrated that the metal, the presence of inhomogeneity in the Schottky barrier, interfacial layer, quantum mechanical reflections and tunnel of carrier, can cause some variation.

According to (2.45),  $J_{S\to M}$  depends on the Schottky barrier height, but not to its shape and it strongly depends on the applied voltage bias, being exponentially increased (decreased) by positive (negative) bias. The total density current through the junction is equal to the sum of the density current from the metal to the semiconductor  $(J_{M\to S})$  and the density current from the semiconductor to the metal  $(J_{S\to M})$ . Since the metal workfunction is bias independent,  $J_{MS}$  can be determinate by applying the equilibrium condition  $(V = 0 \ V)$ :

$$J_{M \to S} + J_{S \to M} = 0 (2.47)$$

$$J_{M\to S} = -J_{S\to M} = A^* T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right). \tag{2.48}$$

The total current density is then

$$J_n = \left[ A^* T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right) \right] \left[ \exp\left(\frac{qV}{kT}\right) - 1 \right]$$

$$=J_0 \left[ \exp\left(\frac{qV}{kT}\right) - 1 \right],\tag{2.49}$$

where

$$J_0 \equiv A^* T^2 \exp\left(-\frac{q\phi_{Bn}}{kT}\right) \tag{2.50}$$

is the saturation density current.

#### 2.5.2 Tunneling Current

In the case of high doped semiconductor and/or for operation at low temperatures, the tunneling current may become significant. The tunneling current from the semiconductor to the metal  $J_{S\to M}$  is proportional to the quantum transmission coefficient (tunneling probability) multiplied by the occupation probability in the semiconductor and the unoccupied probability in the metal, that is,

$$J_{S \to M} = \frac{A^* T^2}{kT} \int_{E_{FM}}^{q\phi_{Bn}} F_S T(E) (1 - F_M) dE.$$

(2.51)

$F_S$  and  $F_M$  are the Fermi-Dirac distribution functions for the semiconductor and the metal respectively, and T(E) is the tunneling probability which depends on the width of the barrier at a particular energy. The density current from the metal to the semiconductor is similar to (2.51) and flow from the opposite direction.

The tunneling current contribution induced a deviation of the ideal thermionic emission I-V. In forward, the rise of the current can be better described by inserting a phenomenological parameter  $\eta$  in the exponential in equation (2.49)

$$J = J_0 \left[ \exp\left(\frac{qV}{\eta kT}\right) - 1 \right] \tag{2.52}$$

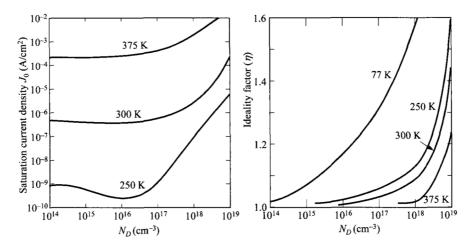

$\eta$  is known as ideality factor. In Fig. 18 are plotted the current density  $J_0$  and  $\eta$  for Au-Si diode as a function of doping concentration.  $J_0$  is constant for low doping, but starts to increase rapidly when  $N_D > 10^{17} cm^{-3}$ .  $\eta$  is very close to unity at low doping and high temperature, but it begins to increase at higher doping concentration and lower temperature.

Fig. 18 Density saturation current  $J_0$  and ideality factor  $\eta$  as function of the doping concentration.

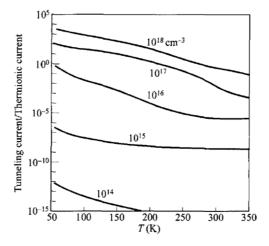

In Fig. 19 is shown the ratio of the tunneling current to the thermionic of an Au-Si barrier diode. For doping concentration  $N_D \leq 10^{17} cm^{-3}$  and T > 300K, the ratio is much less than unity and the tunneling current component can be neglected. While at higher doping level and lower temperature, the ratio can become much larger than unity, indicating that the tunneling current becomes dominant.

Fig. 19 Ratio of the tunneling current to the thermionic current in Au-Si Schottky junction.

## 2.5.3 Effect of the bias dependence of Schottky barrier

In the previous paragraphs, we determinated the thermionic density current equation and we introduced the ideality factor to consider the contribution from the tunneling density current. The ideality factor can be also used to consider other phenomena such as the lowering barrier effect induced by the applied bias.

Let us consider the general case of either n-type or p-type semiconductor, and suppose that  $\phi_B$  depends linearly on the applied bias V, which is true for small value of V, so that we can write

$$\phi_B = \phi_{B0} + \beta V \tag{2.53}$$

$\beta$  is positive because  $\phi_B$  increases with increasing forward bias. We can rewrite (2.49) as

$$J = A^* T^2 \exp\left[-\frac{q(\phi_{B0} + \beta V)}{kT}\right] \left[\exp\left(\frac{qV}{kT}\right) - 1\right]$$

$$= J_0 \exp\left(-\frac{q\beta V}{kT}\right) \left[\exp\left(\frac{qV}{kT}\right) - 1\right]$$

(2.54)

Equation (2.54), can be rewritten as

$$J = J_0 \exp\left(\frac{qV}{nk}\right) \left[1 - \exp\left(-\frac{qV}{kT}\right)\right]$$

(2.55)

where

$$\frac{1}{\eta} = 1 - \beta = 1 - \frac{\partial \phi_B}{\partial V} \tag{2.56}$$

#### 2.5.4 MIS Tunnel Diode

Until now we have considered ideal homogeneous metal semiconductor junction. In reality, a thin layer of oxide is usually introduced before the metal deposition. This interfacial layer thickness lies in the rage of  $1 - 3 \, nm$ . The presence of an oxide layer (1) reduces the current, (2) forms a lower barrier height and (3) higher ideality factor  $\eta$ .

The density current equation (2.52) can be rewritten by introducing a tunneling attenuation factor  $\exp(-\sqrt{\chi} \cdot \delta)$  where  $\chi$  (in eV) is the effective barrier,  $\delta$  (in Å) is the thickness of the interfacial layer and  $C = [2(2m_e^*/\hbar^2)]^{1/2} \approx 1.01 \ eV^{-1/2} \text{Å}^{-1/2}$ :

$$J = A^*T^2 \exp\left(-\sqrt{\chi} \cdot \delta \cdot C\right) \exp\left(-\frac{q\phi_B}{kT}\right) \left[\exp\left(\frac{qV}{nkT}\right) - 1\right]$$

(2.57)

C is usually omitted

$$J = A^*T^2 \exp\left(-\sqrt{\chi} \cdot \delta\right) \exp\left(-\frac{q\phi_B}{kT}\right) \left[\exp\left(\frac{qV}{\eta kT}\right) - 1\right]$$

(2.58)

The ideality factor  $\eta$  is increased to

$$\eta = 1 + \left(\frac{\delta}{\varepsilon_i}\right) \frac{\left(\frac{\varepsilon_S}{W_D}\right) + qD_{its}}{1 + \left(\frac{\delta}{\varepsilon_i}\right) qD_{itm}}$$

(2.59)

where  $D_{its}$  and  $D_{itm}$  are interface traps in equilibrium with the semiconductor and metal, respectively. When the oxide layer is less than 3 nm, the interface traps are in equilibrium with the metal, while for thicker oxides the traps tend to be in equilibrium with the semiconductor.

In conclusion the interfacial layer reduces the majority carrier thermionic emission current, but it doesn't affect the minority carrier current, which is from diffusion, and raises the

minority injection efficiency. This phenomenon is exploited to improve the Schottky solar cell open-circuit voltage.

## 2.6 Measurement of the Schottky parameters

Determining the Schottky diode parameters, which must be considered in practical application, plays an important role in the designing and manufacturing process.

We previously described the forward bias J-V characteristic for ideal diode, equation (2.52), in this case we will consider the real case and thus the potential drop due to the series resistance  $(R_S)$ . Let's rewrite equation (2.52) by taking into account also the surface junction A,

$$J \cdot A \equiv I = I_0 \left[ \exp\left(\frac{q(V - IR_S)}{\eta kT}\right) - 1 \right]$$

(2.60)

where  $I_0$  is the saturation current defined as

$$I_0 = AA^*T^2 \exp\left(-\frac{q\phi_B}{kT}\right). \tag{2.61}$$

$q\phi_B$  can be easily extracted from the reverse saturation current (2.61) when all variable are known. Eq. (2.61) allows to determinate the  $q\phi_B$  when all other parameters are known, but it does not give any information about the quality of the junction ( $\eta$ ).

Let's consider the range where the series resistance  $R_S$  can be neglected  $(V \gg IR_S)$ , equation (2.60) can be rewritten in the form of

$$\ln(I) = \ln(I_0) + \frac{qV}{\eta kT}.$$

(2.62)

By doing so, we obtain a linear relation between the diode logarithmic current and the voltage. The reverse saturation current and the ideality factor can be extracted from the linear fit intercept and slope, respectively. Once the  $I_0$  is obtained, the  $q\phi_B$  can be extrapolated from (2.61). This analysis is quite simple and allows to extrapolate the Schottky barrier easily if  $A^*$  is known. Although  $A^*$  values are reported for every semiconductor [102], the presence of an insulator layer in the junction (see paragraph 2.5.4) or inhomogeneity can reduce it making the  $q\phi_B$  obtained inaccurate. By rewriting equation (2.61) in the form of

$$\ln \frac{I_0}{T^2} = \ln(AA^*) - \frac{q\phi_B}{kT}.$$

(2.63)

we obtain the Arrhenius plot where the Richardson constant and the Schottky barrier can be extrapolated from the its intercept and slope, respectively.  $I_0$  are the reverse saturation currents obtained from the linear fit of equation (2.62) performed on the ln(I)-V measured at different temperatures T.

We have to determinate now the series resistance.

Unfortunately, the determination of the  $R_S$  is not a simple task, equation (2.60) is in fact, a transcendental equation. Therefore, the  $R_S$  cannot be determinated analytically but it can be approximated. Different methods were proposed, most of them use some auxiliary function, such as the derivative or the integration of the current with respect to the voltage and several I-V measurements at different temperatures [105]. We will not focus on all of them, but the one we used in this work, i.e. the Cheung and Cheung method and the Lien-Norde method.

### 2.6.1 The Cheung and Cheung method

Another way to determinate the Schottky diode parameters was proposed by S.K. Cheung and N. W. Cheung in 1986 [106]. The Cheung and Cheung (C.C.) method allows the determination of the Schottky barrier, the ideality factor and the series resistance value at different temperatures.

Let's consider equation (2.60) and rewrite it in the form

$$V = R_S I + \eta \phi_B + \left(\frac{\eta}{kT}\right) \ln\left(\frac{I}{AA^*T^2}\right),\tag{2.64}$$

Differentiating equation (2.64) with respect to  $\ln I$  we obtain

$$\frac{d(V)}{d(\ln I)} = R_S I + \frac{\eta}{kT},\tag{2.65}$$

the  $R_S$  and the  $\eta$  can be determinated from the slope and the intercept respectively. The determination of the Schottky barrier can be done by defining the function H(I) as

$$H(I) \equiv V - \left(\frac{\eta}{kT}\right) \ln\left(\frac{I}{AA^*T^2}\right),\tag{2.66}$$

From equation (2.64) we obtain

$$H(I) = R_{\rm S}I + \eta \phi_{\rm R} \tag{2.67}$$

Once the ideality factor is determined, the right side of Equation (2.66) can be computed. According to Equation (2.67), the H(I) vs. I plot is a straight line whose slope and intercept are the  $R_S$  and the product  $\eta \phi_B$ , respectively. The  $R_S$  obtained from equation (2.67) can be used to check the consistency of this approach.

This method allows to determinate the  $R_S$ , the  $\eta$ , and the  $\phi_B$  value at different temperature which is of great help to better understand how the Schottky parameters vary from low to high temperatures.

### 2.6.2 Lien-Norde method

The presence of a series resistance  $R_S$  affect the forward current by reducing the interval where the I-V plot is linear. Furthermore, since one is forced to use a range where the bias V is small, recombination current in the diode may be a significant part of the total current making the extrapolated  $I_0$  value still more unreliable.

The Lien-Norde method allow to determinate the Schottky diode parameters using the ideality factor  $\eta$  determinated from the T.E. model and the function F(V) defined as [107,108]

$$F(V) = \frac{V}{\gamma} - \frac{1}{kT} \ln \left( \frac{I(V)}{AA^*T^2} \right). \tag{2.68}$$

where  $\gamma$  is an arbitrary constant greater than the ideality factor. The  $\phi_B$  and the  $R_S$  can be determinated as

$$q\phi_B = F(V_{min}) + \frac{\gamma - \eta}{\eta} \left( \frac{V_{min}}{\gamma} - \frac{kT}{q} \right)$$

(2.69)

$$R_S = \frac{(\gamma - \eta)kT}{qI_{min}} \tag{2.70}$$

where  $F(V_{min})$  and  $V_{min}$  are the coordinates of the minimum point in the plot F(V) vs V and  $I_{min}$  is the current value at the voltage  $V_{min}$ . The accuracy of this method is strictly related to the independence from the parameter  $\gamma$ .

### 2.6.3 Pros and cons of the methods

All the method listed before cannot be used as stand alone. Some of them can be used to determinate some parameters while other cannot. An example is the Richardson constant  $A^*$ . When  $A^*$  is unknown it cannot be determinated using the C.C. method and the Norde method, but it can only be determinated from the thermionic emission model. In the same way,  $R_S$  cannot be determinated from the thermionic emission model but it can be determinated from the C.C. and Norde method.

## 2.7 Capacitance-Voltage measurement

The Schottky barrier can be determinate from the I-V characteristic using different method, but it can also determinate from the C-V characteristic. When a small AC voltage is applied upon a DC bias, incremental charges of one sign are induced on the metal surface and charges of the opposite sign in the semiconductor. From equation (2.14) we obtain a linear plot of  $1/C^2$  vs V. The intercept plot gives the built-in potential  $\psi_{bi}$  from which the barrier height can be determinate:

$$\phi_B = \psi_{bi} + \phi_n + \frac{kT}{q} - \Delta\phi \tag{2.71}$$

From the slope the carrier density can also be determinate (2.15) and it can be used to calculate  $\phi_n$ .

# 3 Graphene/Silicon Junction

## 3.1 Modelling of Graphene/Silicon Junction

A theory able to fully describe the graphene/Silicon junction does not exist to-date, although few phenomenological models, explaining experiment features, have been proposed.

S. Tongay et al. tried first to propose a simple modification of the thermionic emission theory to include the bias dependence of the  $E_F$  and explain the bias driven-increase of the reverse saturation current [46]. In a metal/semiconductor junction the metal Fermi level stays constant upon the application of a bias because of the high density of states of the metal. When the metal is replaced with graphene, there is an exchange of charges between the 2D graphene and a 3D silicon.

Let's consider the band structure of the junction formed by a graphene and a n-doped silicon substrate (Fig. 20 (a)). Let assume the graphene Fermi level ( $E_F$ ) is a t Dirac point and it is aligned with silicon Fermi level ( $E_{FS}$ ). The Schottky barrier  $\Phi_B$  will be

$$\Phi_B = \Phi_g - \chi \tag{3.1}$$

where  $\Phi_g$  is the graphene workfunction and  $\chi$  is the silicon electron affinity.

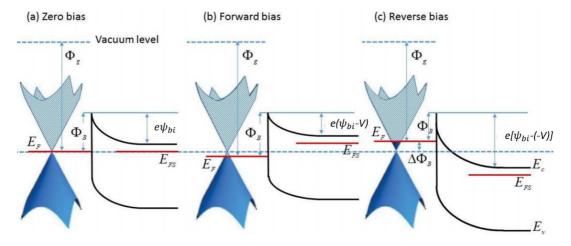

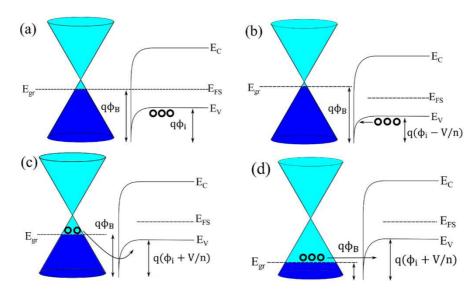

Let us suppose the silicon is grounded, and a bias is applied on the graphene. In forward bias, the graphene Fermi level has to shift down to accept the negative charges mirroring the positive on in the depletion layer (Fig. 20 (b)). The effect is small since a low bias is usually applied in forward. Because of that, the Schottky barrier will be a little higher than the equilibrium. In reverse bias (Fig. 20 (c)), the depletion layer increase substantially and so does the negative charges in graphene shifting the Fermi level up. The Schottky barrier will be lower than the equilibrium.

Fig. 20 (a) Band structure of the Gr/Si junction at thermal equilibrium and at 0 V,(b) in forward bias and (c) in reverse bias.

The graphene Fermi level variation due to the bias can be easily included in the thermionic emission model, we introduced before for the Schottky diode, by replacing the constant Schottky barrier with a bias dependent one.

Let's suppose the band alignment hold at zero bias, the graphene carrier density per unit area  $(n_i)$  induced by a bias (V) can be expressed by assuming that it is opposite to the density of the positive ion in the depletion layer. From equation (1.12),  $n_{in}$  is

$$n_{in}(V) = -\Delta n_{depl}$$

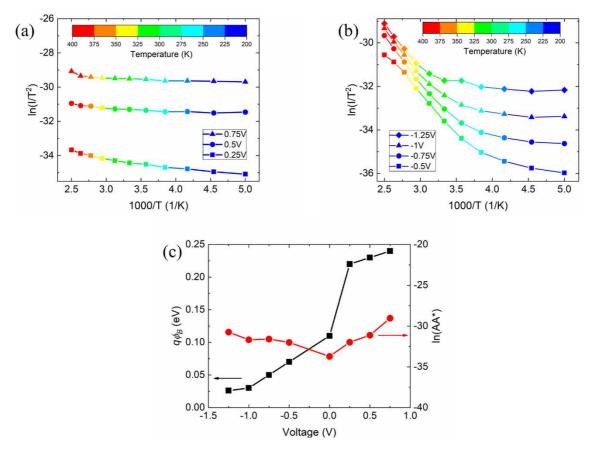

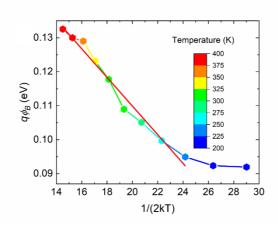

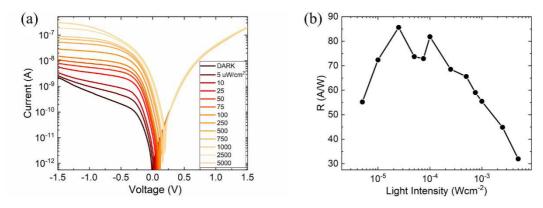

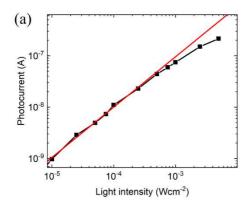

$$= -\left(\sqrt{\frac{2\varepsilon_{S}N_{D}\left(\psi_{bi} - V - \frac{kT}{e}\right)}{e}} - \sqrt{\frac{2\varepsilon_{S}N_{D}\left(\psi_{bi} - \frac{kT}{e}\right)}{e}}\right) (3.2)$$